# MLSoC<sup>™</sup> Development Kit 2.0

Product Brief

# **Highlights**

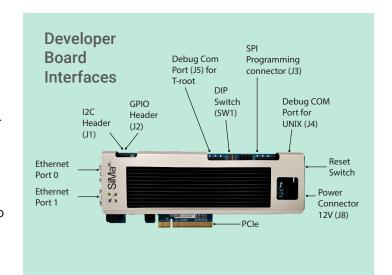

SiMa.ai's MLSoC Development Kit 2.0 contains everything you need to evaluate, prototype and demonstrate standalone on the developer board your computer vision ML applications using the ML purpose built silicon from SiMa.ai. The Development Kit combines a compact Developer Board based on our HHHL PCIe production board and our Palette<sup>TM</sup> software development platform. The Developer board exposes interfaces shown in the figure below and accommodates stand-alone operation on a lab bench environment as well as embeddable in a PCIe platform. These on-bench or PC configuration options offer flexibility to support different developer profiles.

### **Out-of-Box**

Developers want to get the tools and hardware up and running quickly so they can evaluate and learn the new SiMa.ai edge ML platform. The Development Kit provides an Out-of-Box set of components, including software, cables and power supply that you need to make this a breeze and let your developer focus on their application.

#### **Evaluate**

The first step an ML developer will want to do is establish the ML model performance and accuracy on a target platform and assess the capabilities, time and effort in compiling models of interest. Palette provides quantization and compilation of a developers model. Utilize Palette's silicon software image build and deploy tools to program the developer board. The development kit provides the ability to execute these builds and provide KPIs such as; frames per second (fps), latency, accuracy, % loading of compute resources and memory footprint. Palette, running in a Docker on a desktop, supports ARM cross compilation with libraries to generate code for the MLSoC, a platform image build, deploy and test tool suite to create complete ML applications.

## **Prototype:**

The next step an ML developer will want to do is integrate this model into a potential application or use case, including ML model pre- and post- processing functions. To accelerate the prototyping phase, Palette adds the ability to quickly code, build and evaluate a pipeline using your own ML models, using Python coding with our Python APIs for the functional pipeline, for fast proof-of-concepts design without avoiding the complex embedded optimization often needed for on-device execution. These APIs bind your python code to the device execution environment and will execute on device as a complete functioning pipeline. Pushbutton image build and deploy loads this image ion to the developer evaluation board for execution. This proof of concept application can validate the functionality of the pipeline as well as provide an early demonstration vehicle.

#### **Demonstrate**

Quickly bring a real-time video stream to the platform and display the performance results running on the MLSoC silicon for use case demonstrations. The GStreamer based example pipelines can be run out of the box to demonstrate real-time video rate performance. Customer can leverage these pipeline designs to take advantage of the GStreamer pipelining to get higher utilization of compute resources and higher FPS pipeline performance. The developer board processes the pipelines and displays the metadata overlaid on the host PC. Add up to two Ethernet cameras directly or four PCle sourced camera streams to provide multi-camera capabilities.

#### **Key Features**

- On-bench: PCIe edge connector covered in protective coating and four footings to board, USB connector to provide power for stand-alone operation on a bench

- In PC: PCle form factor (68.9mm x 160mm) with standard 98-pin PCB edge connector to interface with any standard host PC or motherboard. Bracket to assist in securing to PC included as option.

- Low Power: Typical workloads 10-15W. Supports PCIe Gen 4.0 up to x8 lanes, LPDDR4 x4, I2C x2, eMMC, μSD card, QSPI-8 x1, 1G Ethernet x2 ports via RJ45, UART x1, and GPIO interfaces.

- Machine Learning Accelerator (MLA): Provides up to 50 Tera Ops Per Second (50 TOPS) for neural network computation.

- Application Processing Unit (APU): A cluster of four ARM Cortex-A65 dual threaded processors operating up to 1.15 GHz to deliver up to 15K Dhry stone MIPs that eliminates the need for an external CPU processor.

- Video Encoder/Decoder: Supports the H.264

compression standards HEVC (High Efficiency Video

Coding) with support for baseline/main/high profiles,

4:2:0 pixels and 8-bit precision. The encoder supports

rates up to 4K P30, while the decoder supports up to 4K

P60.

- Computer Vision Unit (CVU): Consists of a four core Synopsys ARC EV74 video processor supporting up to 600 16-bit GOPS.

- Designed to offer the highest performance for low power embedded edge machine learning applications.

- · HHHL Developer Board

- · Palette Software single seat license

- Type C power adaptor and Type C-cable

- · Ethernet cable

- · UART cable

- PCle mounting bracket

## **Ordering Information**

MLSoC Development Kit 2.0

SKU# MLSoC-DEV-16GB-200-AB

MLSoC Development Kit 2.0 with Ethernet Camera

SKU # MLSOC-DEV-16GB-200-ABA

On-Site Accelerate Board Bring Up and Training day

MLSoC-DBBU-SW-Training-OA

#### About SiMa.ai

SiMa.ai is a machine learning company delivering the industry's first software-centric purpose-built MLSoC platform. For more information, visit www.SiMa.ai.

## **Included in Development Kit 2.0**

Please contact us for more details.

SiMa Technologies, Inc. 333 W. San Carlos St. Suite 1100 MLSoC@sima.ai